Background

In 1972, Intel launched the 8008, the first 8-bit microprocessor. It implemented an instruction set designed by Datapoint corporation with programmable CRT terminals in mind, that also proved to be fairly general purpose. The device needed several additional ICs to produce a functional computer, in part due to its small 18-pin "memory-package" which prevented a separate address bus (Intel was primarily a DRAM manufacturer at the time).

Two years later, in 1974, Intel launched the 8080, employing the new 40-pin DIL packages originally developed for calculator ICs to enable a separate address bus. It had an extended instruction set that was source- (not binary-) compatible with the 8008 and also included some 16-bit instructions to make programming easier. The 8080 device, often described as the first truly useful microprocessor, was nonetheless soon replaced by the 8085 which could cope with a single 5V power supply instead of the three voltages of earlier chips.[5] Other well known 8-bit microprocessors that emerged during these years were Motorola 6800 (1974), Microchip PIC16X (1975), MOS Technology 6502 (1975), Zilog Z80 (1976), and Motorola 6809 (1977), as well as others.

The first x86 design

The 8086 was originally intended as a temporary substitute for the ambitious iAPX 432 project in an attempt to draw attention from the less-delayed 16 and 32-bit processors of other manufacturers (such as Motorola, Zilog, and National Semiconductor) and at the same time to top the successful Z80 (designed by former Intel employees). Both the architecture and the physical chip were therefore developed quickly (in a little more than two years[6]), using the same basic microarchitecture elements and physical implementation techniques as employed for the one year earlier 8085, which it would also function as a continuation of. Marketed as source compatible, it was designed so that assembly language for the 8085, 8080, or 8008 could be automatically converted into equivalent (sub-optimal) 8086 source code, with little or no hand-editing. This was possible because the programming model and instruction set was (loosely) based on the 8085. However, the 8086 design was expanded to support full 16-bit processing, instead of the fairly basic 16-bit capabilities of the 8080/8085. New kinds of instructions were added as well; self-repeating operations and instructions to better support nested ALGOL-family languages such as Pascal, among others.

The 8086 was sequenced using a mix of random logic and microcode and was implemented using depletion load nMOS circuitry with approximately 20,000 active transistors (29,000 counting all ROM and PLA sites). It was soon moved to a new refined nMOS manufacturing process called HMOS (for High performance MOS) that Intel originally developed for manufacturing of fast static RAM products. This was followed by HMOS-II, HMOS-III, and eventually a CMOS version. The original chip measured 33 mm² and minimum feature size was 3.2 μm.

The architecture was defined by Stephen P. Morse and Bruce Ravenel. Peter A.Stoll was lead engineer of the development team and William Pohlman the manager. While less known than the 8088 chip, the legacy of the 8086 is enduring; references to it can still be found on most modern computers in the form of the Vendor ID entry for all Intel devices, which is 8086H (hexadecimal). It also lent its last two digits to Intel's later extended versions of the design, such as the 286 and the 386, all of which eventually became known as the x86 family.

Architecture

Details

Buses and operation

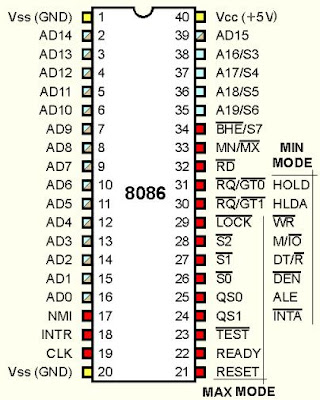

All internal registers as well as internal and external data buses were 16 bits wide, firmly establishing the "16-bit microprocessor" identity of the 8086. A 20-bit external address bus gave an 1 MB (segmented) physical address space (220 = 1,048,576). The data bus was multiplexed with the address bus in order to fit a standard 40-pin dual in-line package. 16-bit I/O addresses meant 64 KB of separate I/O space (216 = 65,536). The maximum linear address space were limited to 64 KB, simply because internal registers were only 16 bits wide. Programming over 64 KB boundaries involved adjusting segment registers (see below) and were therefore fairly awkward (and remained so until the 80386).

Some of the control pins, which carry essential signals for all external operations, had more than one function depending upon whether the device was operated in "min" or "max" mode. The former were intended for small single processor systems whilst the latter were for medium or large systems, using more than one processor.

Registers and instructions

The 8086 had eight (more or less general) 16-bit registers including the stack pointer, but excluding the instruction pointer, flag register and segment registers. Four of them (AX,BX,CX,DX) could also be accessed as (twice as many) 8-bit registers (AH,AL,BH,BL, etc), the other four (BP,SI,DI,SP) were 16-bit only .

Due to a compact encoding inspired by 8085 and other 8-bit processors, most instructions were one-address or two-address operations which means that the result were stored in one of the operands. At most one of the operands could be in memory, but this memory operand could also be the destination, while the other operand, the source, could be either register or immediate. A single memory location could also often be used as both source and destination which, among other factors, further contributed to a code density comparable to (often better than) most eight bit machines.

Although the degree of generality of most registers were much greater than in the 8080 or 8085, it was still fairly low compared to the typical contemporary minicomputer, and registers were also sometimes used implicitly by instructions. While perfectly sensible for the assembly programmer, this complicated register allocation for compilers compared to more regular 16- and 32-bit processors (such as the PDP-11, VAX, 68000, etc); on the other hand, compared to contemporary 8-bit microprocessors (such as the 8085, or 6502), it was significantly easier to generate code for the 8086 design.

As mentioned above 8086 also featured 64 KB of 8-bit (or alternatively 32 K-word or 16-bit) I/O space. A 64 KB (one segment) stack growing towards lower addresses is supported by hardware; 2-byte words are pushed to the stack and the stack top (bottom) is pointed out by SS:SP. There are 256 interrupts, which can be invoked by both hardware and software. The interrupts can cascade, using the stack to store the return address.

The processor had some new instructions (not present in the 8085) to better support stack based high level programming languages such as Pascal and PL/M; some of the more useful ones were push mem-op, and ret size, supporting the "pascal calling convention". (Several others, such as push immed and enter, would be added in the subsequent 80186, 80286, and 80386 designs.)

Segmentation

There were also four sixteen-bit segment registers (CS, DS, SS, ES, standing for "code segment", "data segment", "stack segment" and "extra segment") that allowed the CPU to access one megabyte of memory in an unusual way. Rather than concatenating the segment register with the address register, as in most processors whose address space exceeded their register size, the 8086 shifted the segment register left 4 bits and added it to the offset address (physical address = 16·segment + offset), producing a 20-bit effective address from the 32-bit segment:offset pair. As a result, each physical address could be referred to by 212 = 4096 different segment:offset pairs. This scheme had the advantage that a small program (less than 64 kilobytes) could be loaded starting at a fixed offset (such as 0) in its own segment, avoiding the need for relocation, with at most 15 bytes of alignment waste. The 16-byte separation between segment bases was known as a "paragraph".

Compilers for the 8086 commonly supported two types of pointer, "near" and "far". Near pointers were 16-bit addresses implicitly associated with the program's code or data segment (and so made sense only in programs small enough to fit in one segment). Far pointers were 32-bit segment:offset pairs. C compilers also supported "huge" pointers, which were like far pointers except that pointer arithmetic on a huge pointer treated it as a flat 20-bit pointer, while pointer arithmetic on a far pointer wrapped around within its initial 64-kilobyte segment.

To avoid the need to specify "near" and "far" on every pointer and every function which took or returned a pointer, compilers also supported "memory models" which specified default pointer sizes. The "small", "compact", "medium", and "large" models covered every combination of near and far pointers for code and data. The "tiny" model was like "small" except that code and data shared one segment. The "huge" model was like "large" except that all pointers were huge instead of far by default. Precompiled libraries often came in several versions compiled for different memory models.

In principle the address space of the x86 series could have been extended in later processors by increasing the shift value, as long as applications obtained their segments from the operating system and did not make assumptions about the equivalence of different segment:offset pairs. In practice the use of "huge" pointers and similar mechanisms was widespread, and the shift value was never changed.

According to Morse et al, the designers of the 8086 considered using a shift of eight bits instead of four, which would have given the processor a 16-megabyte address space.

Interview Questions

1.What are the flags in 8086?

- In 8086 Carry flag, Parity flag, Auxiliary carry flag, Zero flag, Overflow flag, Trace flag, Interrupt flag, Direction flag, and Sign flag.

2.What are the various interrupts in 8086?

- Maskable interrupts, Non-Maskable interrupts.

3.What is meant by Maskable interrupts?

- An interrupt that can be turned off by the programmer is known as Maskable interrupt.

4.What is Non-Maskable interrupts?

An interrupt which can be never be turned off (ie.disabled) is known as Non-Maskable interrupt.

5.Which interrupts are generally used for critical events?

- Non-Maskable interrupts are used in critical events. Such as Power failure, Emergency, Shut off etc.,

6.Give examples for Maskable interrupts?

- RST 7.5, RST6.5, RST5.5 are Maskable interrupts

7.Give example for Non-Maskable interrupts?

- Trap is known as Non-Maskable interrupts, which is used in emergency condition.

8.What is the Maximum clock frequency in 8086?

- 5 Mhz is the Maximum clock frequency in 8086.

9.What are the various segment registers in 8086?

- Code, Data, Stack, Extra Segment registers in 8086.

10.Which Stack is used in 8086?

- FIFO (First In First Out) stack is used in 8086.In this type of Stack the first stored information is retrieved first.

11.What are the address lines for the software interrupts? -

12.What is SIM and RIM instructions?

- SIM is Set Interrupt Mask. Used to mask the hardware interrupts. RIM is Read Interrupt Mask. Used to check whether the interrupt is Masked or not.

13.Which is the tool used to connect the user and the computer?

- Interpreter is the tool used to connect the user and the tool.

14.What is the position of the Stack Pointer after the PUSH instruction?

- The address line is 02 less than the earlier value.

15.What is the position of the Stack Pointer after the POP instruction?

- The address line is 02 greater than the earlier value.

16.Logic calculations are done in which type of registers?

- Accumulator is the register in which Arithmetic and Logic calculations are done.

17.What are the different functional units in 8086?

- Bus Interface Unit and Execution unit, are the two different functional units in 8086.

18.Give examples for Micro controller?

- Z80, Intel MSC51 &96, Motorola are the best examples of Microcontroller.

19.What is meant by cross-compiler?

- A program runs on one machine and executes on another is called as cross-compiler.

20.What are the address lines for the hardware interrupts? -

21.Which Segment is used to store interrupt and subroutine return address registers?

- Stack Segment in segment register is used to store interrupt and subroutine return address registers.

22.Which Flags can be set or reset by the programmer and also used to control the operation of the processor?

- Trace Flag, Interrupt Flag, Direction Flag.

23.What does EU do?

- Execution Unit receives program instruction codes and data from BIU, executes these instructions and store the result in general registers.

24.Which microprocessor accepts the program written for 8086 without any changes?

- 8088 is that processor.

25.What is the difference between 8086 and 8088?

- The BIU in 8088 is 8-bit data bus & 16- bit in 8086.Instruction queue is 4 byte long in 8088and 6 byte in 8086.

how to design a fully buffered 8086 system in minimum mode of operation by using block diagram of 8086 microprocessor, clock generator, latches and buffer. and how to demonstrate the design.

ReplyDeleteI did'nt get wat u mean ?

ReplyDeleteanyway u can model the entire design by using Hardware description Languages like VHDL and Verilog

what are the different types of register in microprocessor

ReplyDeletememory of 8086 is divided into 16 segments,where we use 4 segments of 64KB memory,i.e.,code segment,data segment,stack segment,extra segment which can be used as general purpose registers of 8bit.and different types are accumulator register,base register,counter register,data register.

Delete(A,B,C,D registers)

what are different type of register in 8086 microprocessor

ReplyDeleteGeneral purpose registers:- AX,BX,BP,SP etc

ReplyDeleteSegment registers :- CS,DS,ES,SS

Special purpose reg :- IP

Flag register : "CPASZTIDO"

easy to remind if u pronounce "ceepee asztido"

dat pronounce thing is good thanks ...... any more things likes this which makes remember these things pl put it up

Deletedat pronounce thing is good thanks ...... any more things likes this which makes remember these things plz put it up

Deletewhy do we use 2 ground pins? i.e, 1 and 20th pin as vss(gnd).

ReplyDeletewhy cant we use only one ground and make another pin as no connection?